SVA

Table of Contents

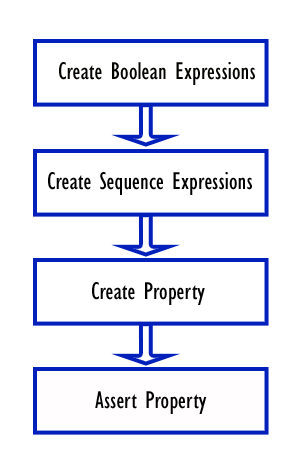

Below diagram shows the steps involved in the creation of an SVA checker,

Boolean expressions

The functionality is represented by the combination of multiple logical events. These events could be simple Boolean expressions.

Sequence

Boolean expression events that evaluate over a period of time involving single/multiple clock cycles. SVA provides a keyword to represent these events called “sequence.”

Syntax

sequence name_of_sequence; …… endsequence

Property

A number of sequences can be combined logically or sequentially to create more complex sequences. SVA provides a keyword to represent these complex sequential behaviors called “property”.

Syntax

property name_of_property; test expression or complex sequence expressions endproperty

Assert

The property is the one that is verified during a simulation. It has to be asserted to take effect during a simulation. SVA provides a keyword called “assert” to check the property.

Syntax

assertion_ name: assert_property( property_name );