Category: SystemVerilog

SystemVerilog Priority if

priority if

Priority if evaluates all the conditions in sequential order.

In the following conditions simulator issue a run time error/warning

- No condition is true or final if doesn’t have corresponding else

priority if examples

In the below example,

No condition is true or final if doesn’t have corresponding else.

value of a=50,b=20 and c=40. conditions a<b and a<c are false,

therefore simulator issue a run time warning.

“RT Warning: No condition matches in ‘priority if’ statement.”

module priority_if;

//variables declaration

int a,b,c;

initial begin

//initialization

a=50;

b=20;

c=40;

priority if ( a < b ) $display("\t a is less than b");

else if ( a < c ) $display("\t a is less than c");

end

endmodule

Simulator Output

RT Warning: No condition matches in 'priority if' statement.

priority if example 2

In the below example,

value of a=10,b=20 and c=40.

conditions a<b and a<c are true, as it is priority based, simulator

considers the first match. therefore there will be no simulator warning message.

module priority_if;

//variables declaration

int a,b,c;

initial begin

//initialization

a=10;

b=20;

c=40;

priority if ( a < b ) $display("\t a is less than b");

else if ( a < c ) $display("\t a is less than c");

else $display("\t a is greater than b and c");

end

endmodule

Simulator Output

a is less than b

SystemVerilog Unique if

unique if

Unique if evaluates all the conditions parallel.

In the following conditions simulator issue a run time error/warning,

- More than one condition is true

- No condition is true or final if doesn’t have corresponding else

Unique if example’s

In the below example,

More than one condition is true.

value of a=10, b=20 and c=40. conditions a<b and a<c are true,

Therefore on execution, simulator issue a run time warning.

“RT Warning: More than one condition match in ‘unique if’ statement.”

module unique_if;

//variables declaration

int a,b,c;

initial begin

//initialization

a=10;

b=20;

c=40;

unique if ( a < b ) $display("\t a is less than b");

else if ( a < c ) $display("\t a is less than c");

else $display("\t a is greater than b and c");

end

endmodule

Simulator Output

a is less than b RT Warning: More than one conditions match in 'unique if' statement.

Unique if example 2

In below example,

No condition is true and final if doesn’t have corresponding else.

value of a=50, b=20 and c=40, conditions a<b and a<c are false,

Therefore on execution, simulator issue a run time warning.

“RT Warning: No condition matches in ‘unique if’ statement.”

module unique_if;

//variables declaration

int a,b,c;

initial begin

//initialization

a=50;

b=20;

c=40;

unique if ( a < b ) $display("\t a is less than b");

else if ( a < c ) $display("\t a is less than c");

end

endmodule

Simulator Output

RT Warning: No condition matches in 'unique if' statement

Unique if example 3

In below example, value of a=50, b=20 and c=40.

conditions a<b and a<c are false, so else part is true, there is no simulator run time warning.

module unique_if;

//variables declaration

int a,b,c;

initial begin

//initialization

a=50;

b=20;

c=40;

priority if ( a < b ) $display("\t a is less than b");

else if ( a < c ) $display("\t a is less than c");

else $display("\t a is greater than b and c");

end

endmodule

Simulator Output

a is greater than b and c

SystemVerilog NonBlocking assignment

nonblocking assignment

- non-blocking assignment statements execute in parallel

- In the non-blocking assignment, all the assignments will occur at the same time. (during the end of simulation timestamp)

Nonblocking assignment example

In the below example,

a and b are initialized with values 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b.

After assignment values expected in a and b are 15 and 20 respectively.

but these values will get assigned only after the simulation time-stamp.

module nonblocking_assignment;

//variables declaration

int a,b;

initial begin //initial block will get executed at starting of simulation

$display("-----------------------------------------------------------------");

//initializing a and b

a = 10;

b = 15;

//displaying initial value of a and b

$display("\tBefore Assignment :: Value of a is %0d",a);

$display("\tBefore Assignment :: Value of b is %0d",b);

a <= b;

b <= 20;

$display("\tAfter Assignment :: Value of a is %0d",a);

$display("\tAfter Assignment :: Value of b is %0d",b);

$display("-----------------------------------------------------------------");

end

final begin //final block will get executed at end of simulation

$display("-----------------------------------------------------------------");

$display("\tEnd of Simulation :: Value of a is %0d",a);

$display("\tEnd of Simulation :: Value of b is %0d",b);

$display("-----------------------------------------------------------------");

end

endmodule

Simulator Output:

----------------------------------------------------------------- Before Assignment :: Value of a is 10 Before Assignment :: Value of b is 15 After Assignment :: Value of a is 10 After Assignment :: Value of b is 15 ----------------------------------------------------------------- ----------------------------------------------------------------- End of Simulation :: Value of a is 15 End of Simulation :: Value of b is 20 -----------------------------------------------------------------

Nonblocking assignment example-2

In the below example,

a and b are initialized with value 10 and 15 respectively.

x<=a+b and y<=a+b+x

value of x is sum of a (10) and b (15). -> x=10+15=25.

value of y is sum of a (10) ,b(15) and x (0) -> became at current simulation time-stamp value of x=0.

new value will get assigned at the end of current time stamp, and new value will be available only after the current time-stamp). therefore y=10+15+0=25;

module nonblocking_assignment;

//variables declaration

int a,b;

int x,y;

initial begin

//initializing a and b

a = 10;

b = 15;

x <= a + b;

y <= a + b + x;

$display("-----------------------------------------------------------------");

$display("\tValue of x is %0d",x);

$display("\tValue of y is %0d",y);

$display("-----------------------------------------------------------------");

end

final begin

$display("-----------------------------------------------------------------");

$display("\tEnd of Simulation :: Value of x is %0d",x);

$display("\tEnd of Simulation :: Value of y is %0d",y);

$display("-----------------------------------------------------------------");

end

endmodule

Simulator Output:

----------------------------------------------------------------- Value of x is 0 Value of y is 0 ----------------------------------------------------------------- ----------------------------------------------------------------- End of Simulation :: Value of x is 25 End of Simulation :: Value of y is 25 -----------------------------------------------------------------

SystemVerilog Blocking assignment

Blocking Assignment

Blocking assignment statements execute in series order. Blocking assignment blocks the execution of the next statement until the completion of the current assignment execution.

Blocking assignment example

In Below Example, a and b is initialized with value 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment value of a = 15 and b=20.

module blocking_assignment;

//variables declaration

int a,b;

initial begin

$display("-----------------------------------------------------------------");

//initializing a and b

a = 10;

b = 15;

//displaying initial value of a and b

$display("\tBefore Assignment :: Value of a is %0d",a);

$display("\tBefore Assignment :: Value of b is %0d",b);

a = b;

b = 20;

$display("\tAfter Assignment :: Value of a is %0d",a);

$display("\tAfter Assignment :: Value of b is %0d",b);

$display("-----------------------------------------------------------------");

end

endmodule

Simulator Output:

----------------------------------------------------------------- Before Assignment :: Value of a is 10 Before Assignment :: Value of b is 15 After Assignment :: Value of a is 15 After Assignment :: Value of b is 20 -----------------------------------------------------------------

Blocking assignment example-2

In Below Example, a and b are initialized with value 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment value of a = 15 and b = 20.

module blocking_assignment;

//variables declaration

int a,b;

int x,y;

initial begin

//initializing a and b

a = 10;

b = 15;

x = a + b;

y = a + b + x;

$display("-----------------------------------------------------------------");

$display("\tValue of x is %0d",x);

$display("\tValue of y is %0d",y);

$display("-----------------------------------------------------------------");

end

endmodule

Simulator Output:

----------------------------------------------------------------- Value of x is 25 Value of y is 50 -----------------------------------------------------------------

Arrays

systemverilog associative array find index

SystemVerilog associative array find_index method

SystemVerilog array Index finder method shall return single or multiple indexes which satisfies the condition.

The condition also shall be single or multiple conditions. multiple conditions can be written on using conditional expressions. example: &&, || etc.

index finder methods

| Method | Description |

|---|---|

| find_index() | returns the indexes of all the elements satisfying the given expression |

| find_first_index() | returns the index of the first element satisfying the given expression |

| find_last_index() | returns the index of the last element satisfying the given expression |

| unique_index() | returns the indexes of all elements with unique values or whose expression is unique |

‘with’ clause is optional for min,max,unique and unique_index methods

associative array find_index example

Below example shows the return of single and multiple index return.

class packet;

int a;

int b;

function void display();

$display("\tValue of a = %0d",a);

$display("\tValue of b = %0d",b);

endfunction

endclass

module assoc_array;

//declaration of array

packet assoc_array[*];

packet pkt;

int count,qu[$],tmp_var;

initial begin

pkt = new();

pkt.a = 8;

pkt.b = 3;

assoc_array[2] = pkt;

pkt = new();

pkt.a = 0;

pkt.b = 6;

assoc_array[5] = pkt;

pkt = new();

pkt.a = 2;

pkt.b = 6;

assoc_array[6] = pkt;

pkt = new();

pkt.a = 1;

pkt.b = 6;

assoc_array[9] = pkt;

//----------------------------------------------------------------------------

//------- Find Index Method -------

//----------------------------------------------------------------------------

//Type-1: returning one matching index

qu = assoc_array.find_index with (item.a == 'h2);

count = qu.size();

for(int i=0;i<count;i++) begin //{

tmp_var = qu.pop_front();

$display("Index of Asoc Array for a == 2 is %0d",tmp_var);

end //}

//Type-2: returning mutiple matching index

qu = assoc_array.find_index with (item.b == 6);

count = qu.size();

for(int i=0;i<count;i++) begin //{

tmp_var = qu.pop_front();

$display("Index of Asoc Array for b == 6 is %0d",tmp_var);

end //}

//Type-3: with multiple conditions

qu = assoc_array.find_index with (item.a == 2 && item.b == 6);

count = qu.size();

for(int i=0;i<count;i++) begin //{

tmp_var = qu.pop_front();

$display("Index of Asoc Array for a == 2, b == 6 is %0d",tmp_var);

end //}

//Type-4: with multiple conditions

qu = assoc_array.find_index with (item.a < 2 && item.b > 5);

count = qu.size();

for(int i=0;i<count;i++) begin //{

tmp_var = qu.pop_front();

$display("Index of Asoc Array for a < 2, b > 5 is %0d",tmp_var);

end //}

end

endmodule

Simulator Output

Index of Asoc Array for a == 2 is 6 Index of Asoc Array for b == 6 is 5 Index of Asoc Array for b == 6 is 6 Index of Asoc Array for b == 6 is 9 Index of Asoc Array for a == 2, b == 6 is 6 Index of Asoc Array for a < 2, b > 5 is 5 Index of Asoc Array for a < 2, b > 5 is 9

For more array manipulation method examples refer to Array Manipulation Methods

SystemVerilog array methods

SystemVerilog array methods

SystemVerilog Array provide several built-in methods to operate on arrays. array methods useful for reordering the array elements, to reduce the array to a single value, finding the index or elements of an array and querying the index and element.

This section provides the links to different type of array manipulation methods, which are array ordering methods, array reduction methods, array locator methods and array iterator indexing methods.

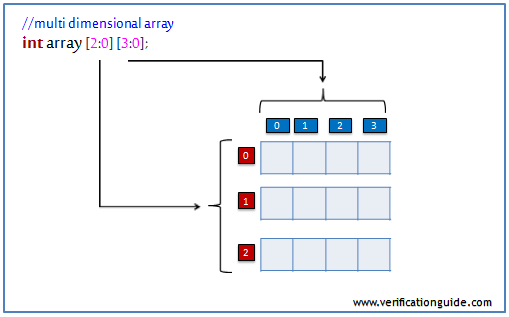

SystemVerilog 2d array

SystemVerilog 2d array initialization

The two-dimensional array is an array of arrays. The 2D array is organized as matrices which can be represented as the collection of rows and columns.

SystemVerilog 2D array Syntax

data_type array_name [rows][columns];

SystemVerilog 2D array declaration

int array [2:0][3:0];

The data in a two-dimensional array is stored in a tabular form as shown in the below diagram.

SystemVerilog 2D array initialization

array = '{ '{0,1,2,3},'{4,5,6,7},'{8,9,10,11}};

SystemVerilog 2D array example

module two_d_array;

//declaration of array’s

int array[2:0][3:0]; //2 dimension array

initial begin

//array initialization

array = '{'{0,1,2,3},'{4,5,6,7},'{8,9,10,11}};

//displaying array elements

$display("-------displaying 2d array-------");

foreach(array[i,j]) $display("\t array[%0d][%0d] = %0d",i,j,array[i][j]);

end

endmodule

Simulator Output

-------displaying 2d array------- array3[2][3] = 0 array3[2][2] = 1 array3[2][1] = 2 array3[2][0] = 3 array3[1][3] = 4 array3[1][2] = 5 array3[1][1] = 6 array3[1][0] = 7 array3[0][3] = 8 array3[0][2] = 9 array3[0][1] = 10 array3[0][0] = 11

SystemVerilog Enum example

SystemVerilog enum example’s

enum data type

Example-3 : Enumeration Type [DataTypes]

This example shows an error, in case of automatic increment-value, is the same as the value assigned to another enum member.

module enum_datatype;

//declaration

enum { red=0, green=1, blue=4, yellow, white=5, black=6 } Colors;

initial begin

Colors = Colors.first;

for(int i=0;i<6;i++)

$display("Colors :: Value of %0s is = %0d",Colors.name(),Colors);

end

endmodule

Simulator Output

Error-[ENUMDUPL] Duplicate labels in enum testbench.sv, 9 The enum label 'white' has the value 5 which is duplicate of enum label 'yellow' in the declared enum. 1 error

Example-4 : Enumeration Type [DataTypes]

This example shows declaring new data types using the enumerated type.

module enum_datatype;

//declaration

typedef enum {GOOD, BAD} pkt_type;

pkt_type pkt_a;

pkt_type pkt_b;

initial begin

pkt_a = GOOD;

pkt_b=BAD;

if(pkt_a == GOOD)

$display("pkt_a is GOOD packet");

else

$display("pkt_a is BAD packet");

if(pkt_b == GOOD)

$display("pkt_b is GOOD packet");

else

$display("pkt_b is BAD packet");

end

endmodule

Simulator Output

pkt_a is GOOD packet pkt_b is BAD packet

Example-5 : Enumeration Type [DataTypes]

This example shows how to use enumeration methods.

module enum_datatype;

//declaration

typedef enum { red=0, green, blue=4, yellow, white=10, black } colors;

enum { a, b, c, d, e, f, g } alphabets;

colors first_set;

colors second_set;

initial begin

first_set = first_set.first();

$display("first_set first color is \t %0s, \t Value = %0d", first_set.name(),first_set);

first_set = first_set.last();

$display("first_set last color is \t %0s, \t Value = %0d", first_set.name(),first_set);

second_set = first_set;

$display("second_set color is \t %0s, \t Value = %0d", second_set.name(),second_set);

second_set =second_set.prev(2);

$display("second_set color is \t %0s, \t Value = %0d", second_set.name(),second_set);

second_set =second_set.next(2);

$display("second_set color is \t %0s, \t Value = %0d", second_set.name(),second_set);

$display("Number of members in alphabets is \t %0d",alphabets.num());

$display("Default First members in alphabets is \t %0s , \t value is %0d",alphabets.name(),alphabets);

alphabets=alphabets.next;

$display("Next members in alphabets is \t %0s , \t value is %0d",alphabets.name(),alphabets);

alphabets=alphabets.last;

$display("Last members in alphabets is \t %0s , \t value is %0d",alphabets.name(),alphabets);

alphabets=alphabets.prev(3);

$display("3rd members from last in alphabets is \t %0s , \t value is %0d",alphabets.name(),alphabets);

end

endmodule

Simulator Output

first_set first color is red, Value = 0 first_set last color is black, Value = 11 second_set color is black, Value = 11 second_set color is yellow, Value = 5 second_set color is black, Value = 11 Number of members in alphabets is 7 Default First members in alphabets is a and value is 0 Next members in alphabets is b , value is 1 Last members in alphabets is g , value is 6 3rd members from last in alphabets is d , value is 3

class data type

A Class is a collection of data and a set of subroutines that operate on that data. The data in a class are referred to as class properties, and its subroutines are called methods.A Class is declared using the class…endclass keywords.

Class type example

class packet;

// Properties

bit [31:0] address;

bit [31:0] data ;

// Method

function new();

$display("Inside new Function of packet");

endfunction

endclass : packet

A detailed explanation of Classes is explained in later chapters(SystemVerilog Classes).