Clocking Block

Table of Contents

A clocking block specifies timing and synchronization for a group of signals.

The clocking block specifies,

- The clock event that provides a synchronization reference for DUT and testbench

- The set of signals that will be sampled and driven by the testbench

- The timing, relative to the clock event, that the testbench uses to drive and sample those signals

Clocking block can be declared in interface, module or program block.

Clocking block declaration

clocking cb @(posedge clk); default input #1 output #2; input from_Dut; output to_Dut; endclocking

Clocking block terminologies

Clocking event

The event specification used to synchronize the clocking block, @(posedge clk) is the clocking event.

Clocking signal

Signals sampled and driven by the clocking block, from_DUT and to_DUT are the clocking signals,

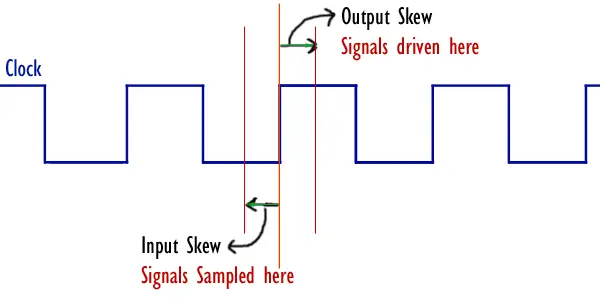

Clocking skew

Clocking skew specifies the moment (w.r.t clock edge) at which input and output clocking signals are to be sampled or driven respectively. A skew must be a constant expression and can be specified as a parameter.

In the above example, the delay values #1 and #2 are clocking skews.

Input and Output skews

Input (or inout) signals are sampled at the designated clock event. If an input skew is specified then the signal is sampled at skew time units before the clock event. Similarly, output (or inout) signals are driven skew simulation time units after the corresponding clock event.

A skew must be a constant expression and can be specified as a parameter. In case if the skew does not specify a time unit, the current time unit is used.

clocking cb @(posedge clk); default input #1ps output #2; input from_Dut; output to_Dut; endclocking //Skew can be specified explicitly to signals: clocking cb @(clk); input #4ps from_Dut; output #6 to_Dut; endclocking

Clocking block events

The clocking event of a clocking block is available directly by using the clocking block name, regardless of the actual clocking event used to declare the clocking block.

For example,

clocking cb @(posedge clk); default input #1 output #2; input from_Dut; output to_Dut; endclocking

The clocking event of the cb clocking block can be used to wait for that particular event:

@( cb );

The above statement is equivalent to @(posedge clk).

Cycle delay: ##

The ## operator can be used to delay execution by a specified number of clocking events, or clock cycles.

Example:

## 8; // wait 8 clock cycles ## (a + 1); // wait a+1 clock cycles