Introduction to UVM

Table of Contents

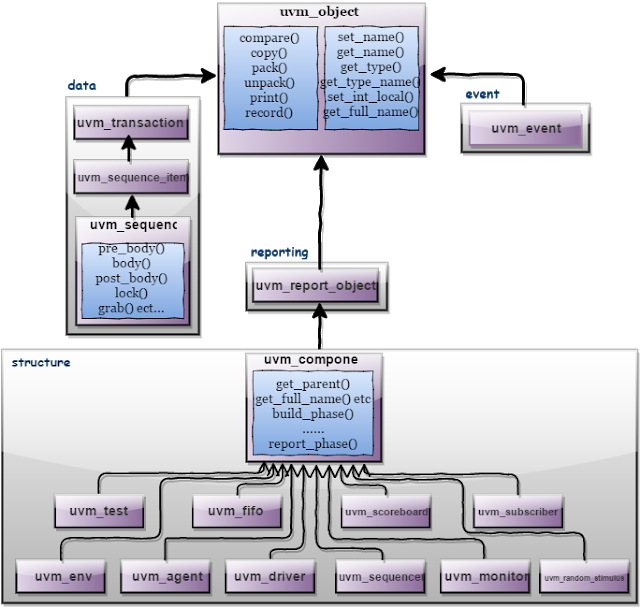

The Universal Verification Methodology (UVM) consists of class libraries needed for the development of well constructed, reusable SystemVerilog based Verification environment.

In simple words, UVM consists of a set of base classes with methods defined in it, the SystemVerilog verification environment can be developed by extending these base classes.

Now on will refer the UVM base classes as UVM Classes.

UVM Classes

UVM consists of three main types of UVM classes,

- uvm_object

- uvm_transaction

- uvm_component

uvm_object

- Core class based operational methods (create, copy, clone, compare, print, record, etc..), instance identification fields (name, type name, unique id, etc.) and random seeding were defined in it.

- All uvm_transaction and uvm_component were derived from the uvm_object.

uvm_transaction

-

- Used in stimulus generation and analysis.

uvm_component

- Components are quasi-static objects that exist throughout the simulation.

- Every uvm_component is uniquely addressable via a hierarchical path name, e.g. “env.agent.driver”.

- The uvm_component also defines a phased test flow, that components follow during the course of the simulation. Each phase(build, connect, run, etc.) is defined by a callback that is executed in precise order.

- The uvm_component also defines configuration, reporting, transaction recording, and factory interfaces.

UVM Class Hierarchy