SystemVerilog TestBench Architecture

Table of Contents

About TestBench

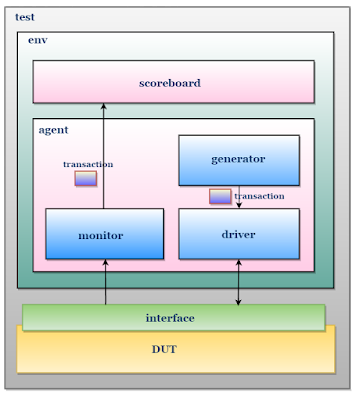

Testbench or Verification Environment is used to check the functional correctness of the Design Under Test (DUT) by generating and driving a predefined input sequence to a design, capturing the design output and comparing with-respect-to expected output.

Verification environment is a group of class’s performing specific operation. i.e, generating stimulus, driving, monitoring, etc. and those classes will be named based on the operation

TestBench Components

| Name | Type | Description |

|---|---|---|

| transaction | class | Defines the pin level activity generated by agent (to drive to DUT through the driver) or the activity has to be observed by agent (Placeholder for the activity monitored by the monitor on DUT signals) |

| generator | class | Generates the stimulus (create and randomize the transaction class) and send it to Driver |

| driver | class | Receives the stimulus (transaction) from a generator and drives the packet level data inside the transaction into pin level (to DUT |

| monitor | class | Observes pin level activity on interface signals and converts into packet level which is sent to the components such as scoreboard |

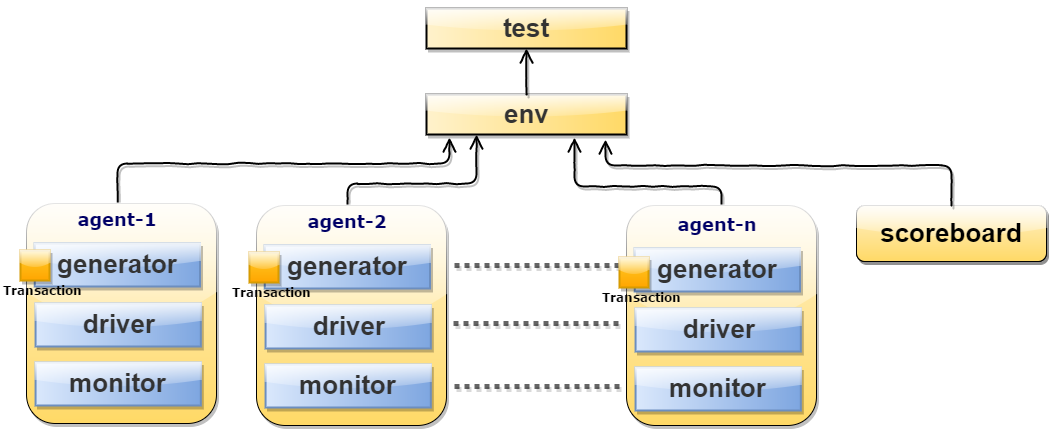

| agent | class | An agent is a container class, which groups the class’s (generator, driver, and monitor) specific to an interface or protocol |

| scoreboard | class | Receives data items from monitors and compares them with expected values. Expected values can be either golden reference values or generated from the reference model |

| environment | class | The environment is a container class for grouping higher level components like agent’s and scoreboard |

| test | program | The test is responsible for,

|

| testbench_top | class | This is the topmost file, which connects the DUT and TestBench. It consists of DUT, Test and interface instances, the interface connects the DUT and TestBench |

TestBench Hierarchy

TestBench Architecture