UVM Register Model Overview

The register model is composed of a hierarchy of blocks that map to the design hierarchy, which means the RAL model consists of equivalent which will refer to the design register fields, registers, and memory.

Blocks can contain,

- registers

- register files

- memories

- other blocks

UVM RAL library provides the base class of each and each class has the default builtin methods in it.

Refer to UVM RAL Base Classes for a detailed description of UVM RAL Base Classes and its Methods.

Register classes cant be used as it is, they must be specialized via extensions to provide an abstract view that corresponds to the design registers and memories.

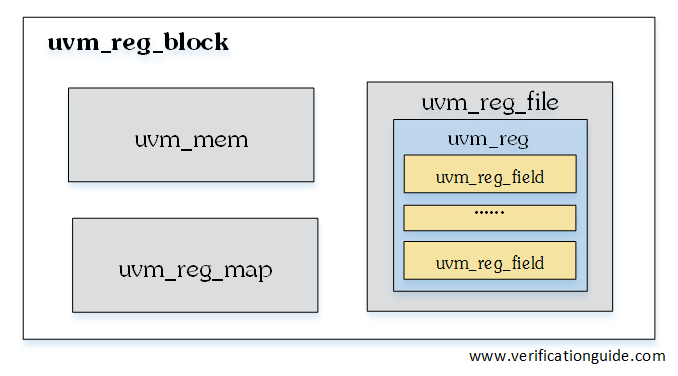

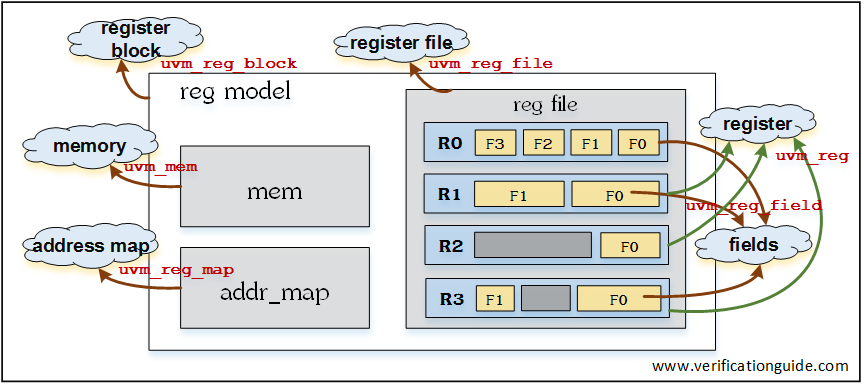

Above block diagram shows that,

- uvm_reg shall consist of one or more uvm_reg_field

- uvm_reg_file shall consist of one or more uvm_reg

- uvm_reg_block shall consist of one or more uvm_reg_file or uvm_mem

Below block diagram shows the mapping of register model components to the environmental components.

Due to a large number of registers in design, this specialization shall be done by a register model generator.

register model generator

Register model generators are outside the scope of the UVM library.

A register model can be written or it can be created using a register generator application. Writing or Generating the register model is based on a design register specification.

Writing a register model is easy, but complex designs will be having hundreds or thousands of registers. in that case, writing the register model is tedious. The easiest way to construct a register model is by using a register generation application or automation tool.

Automation tools will generate the register model by taking register specification as input, this includes reg name, width, register fields, access permissions, etc.

There are paid and free register generators available. some of them are RGM – Register and Memory Package by Cadence, ralgen by Synopsys, Semifore’s RDL, Duolog’s graphical Bitwise, Agnisys’ IDesignSpec, Mentor Graphics’ Certes Testbench Studio, and Magillem MRV (Magillem Register View).

❮ Previous Next ❯