UVM RAL Usage Model

Table of Contents

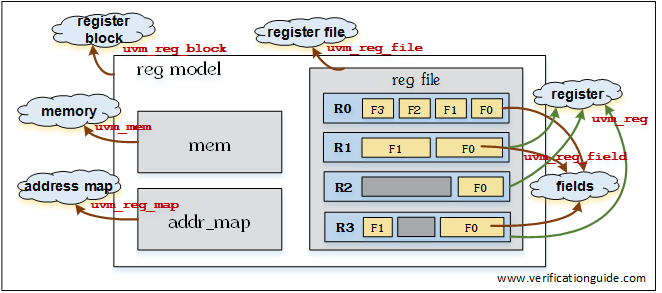

The previous section described the UVM RAL base classes. This section explains using UVM RAL base classes with reference to the design elements. i.e mapping UVM RAL elements with design elements.

Let’s consider the design architecture of the CPU. In this section, In order to understand the use of each UVM RAL element, first, we will map each RAL element with the CPU design elements.

- The architecture of the CPU shows that it consists of multiple modules

- uvm_reg_block shall be used to represent each design module

- each module consists of many registers

- uvm_reg_file shall group the module registers

- each module consists of registers

- uvm_reg shall be used to implement the design register

- each register consists of one or multiple fields

- uvm_reg_field type shall be used for field implementation

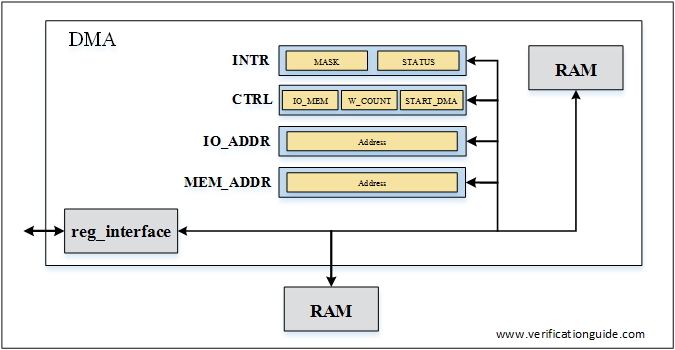

Below block diagram is the Direct Memory Access (DMA) design block containing four registers, which have two, three, one and one fields respectively, an internal memory, and external memory.

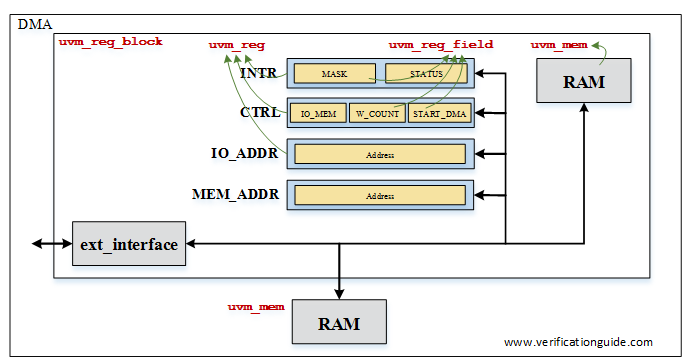

Below block diagram shows the UVM RAL element equivalent to the design element.

RAL Building blocks

- Register block

- Register file

- Register

- Register Filed

Each is explained in detail below,

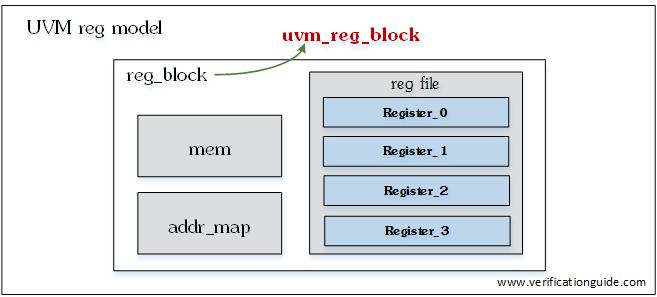

Register Block

The reg block is written by extending the uvm_reg_block.

A block corresponds to a design component/hierarchy with its own interface(s), registers, register files, memories, and sub-blocks.

In simple words, a block can be referred to as a design module with its own interface(s), registers, register files, memories, and sub-blocks. And it will be having unique address decoding to route the access to it.

A register model is an instance of a register block, which may contain any number of registers, register files, memories, and other blocks.

Register File

The reg file is written by extending the uvm_reg_file.

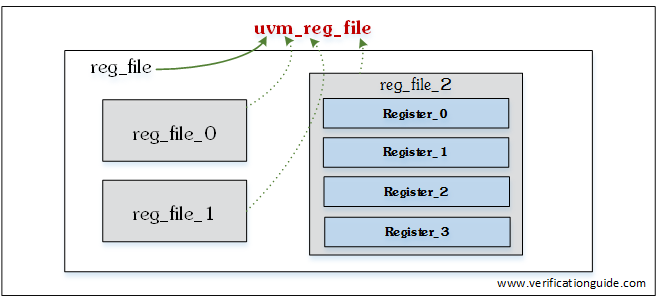

The reg file shall be used to group the number of registers or register files. below block diagram shows the register file consists of reg_file_0, reg_file_1 and reg_file_2. and each register file consists of a set of registers. ( registers are shown only in reg_file_2, Assume that there are registers in reg_file_0 and reg_file_1 )

Register

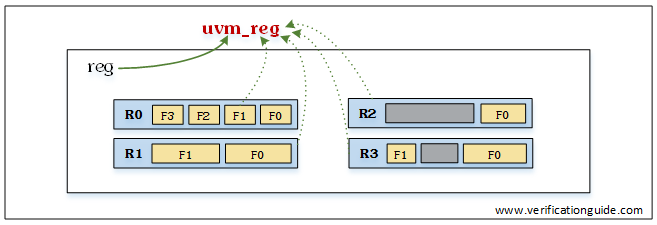

The uvm register class is written by extending the uvm_reg.

A register represents a set of fields that are accessible as a single entity.

Each register contains any number of fields, which mirror the values of the corresponding elements in hardware.

Register Field

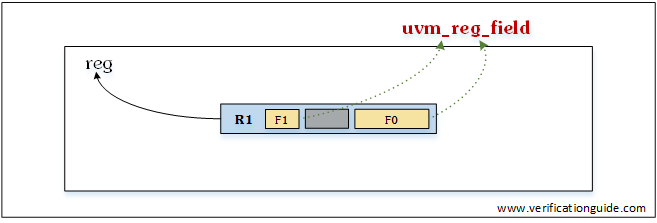

The register field is declared with the type uvm_reg_filed.

Fields represent a contiguous set of bits. All data values are modeled as fields. A field is contained within a single register but may have different access policies. access policies are explained in the next sections.

Complete Register Model block diagram