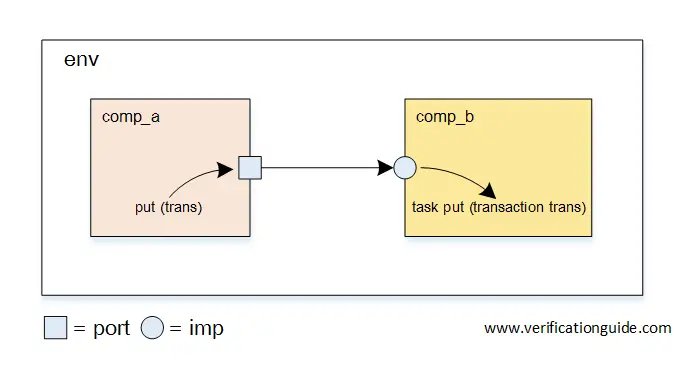

Blocking TLM Port and Blocking Imp Port

Table of Contents

This example shows the blocking nature of blocking port and imp port. This is a continuation of the previous example, Only delay has been added in the blocking put method of comp_b which will lead to a port.put() method call in comp_a to get blocked until the completion of the comp_b put method.

Code

Adding delay in comp_b put method

virtual task put(transaction trans); `uvm_info(get_type_name(),$sformatf(" Recived trans On IMP Port"),UVM_LOW) `uvm_info(get_type_name(),$sformatf(" Before injecting delay"),UVM_LOW) #100; //Delay `uvm_info(get_type_name(),$sformatf(" After injecting delay"),UVM_LOW) `uvm_info(get_type_name(),$sformatf(" Printing trans, \n %s",trans.sprint()),UVM_LOW)endtask |

Simulator Output

UVM_INFO @ 0: reporter [RNTST] Running test basic_test... --------------------------------------------------- Name Type Size Value --------------------------------------------------- uvm_test_top basic_test - @1839 env environment - @1908 comp_a component_a - @1940 trans_out uvm_blocking_put_port - @1975 comp_b component_b - @2008 trans_in uvm_blocking_put_imp - @2043 --------------------------------------------------- UVM_INFO component_a.sv(29) @ 0: uvm_test_top.env.comp_a [component_a] tranaction randomized --------------------------------- Name Type Size Value --------------------------------- trans transaction - @1135 addr integral 4 'he wr_rd integral 1 'h0 wdata integral 8 'h4 --------------------------------- UVM_INFO component_a.sv(32) @ 0: uvm_test_top.env.comp_a [component_a] Before calling port put method UVM_INFO component_b.sv(24) @ 0: uvm_test_top.env.comp_b [component_b] Recived trans On IMP Port UVM_INFO component_b.sv(25) @ 0: uvm_test_top.env.comp_b [component_b] Before injecting delay UVM_INFO component_b.sv(27) @ 100: uvm_test_top.env.comp_b [component_b] After injecting delay UVM_INFO component_b.sv(28) @ 100: uvm_test_top.env.comp_b [component_b] Printing trans, --------------------------------- Name Type Size Value --------------------------------- trans transaction - @1135 addr integral 4 'he wr_rd integral 1 'h0 wdata integral 8 'h4 --------------------------------- UVM_INFO component_a.sv(34) @ 100: uvm_test_top.env.comp_a [component_a] After calling port put method UVM_INFO /playground_lib/uvm-1.2/src/base/uvm_objection.svh(1271) @ 100: reporter [TEST_DONE] UVM_INFO /playground_lib/uvm-1.2/src/base/uvm_report_server.svh(847) @ 100: reporter [UVM/REPORT/SERVER]

Result Analysis

UVM_INFO component_a.sv(32) @ 0: uvm_test_top.env.comp_a [component_a] Before calling port put method UVM_INFO component_b.sv(24) @ 0: uvm_test_top.env.comp_b [component_b] Recived trans On IMP Port UVM_INFO component_b.sv(25) @ 0: uvm_test_top.env.comp_b [component_b] Before injecting delay UVM_INFO component_b.sv(27) @ 100: uvm_test_top.env.comp_b [component_b] After injecting delay UVM_INFO component_b.sv(28) @ 100: uvm_test_top.env.comp_b [component_b] Printing trans, --------------------------------- Name Type Size Value --------------------------------- trans transaction - @1135 addr integral 4 'he wr_rd integral 1 'h0 wdata integral 8 'h4 --------------------------------- UVM_INFO component_a.sv(34) @ 100: uvm_test_top.env.comp_a [component_a] After calling port put method

comp_a code,

32. `uvm_info(get_type_name(),$sformatf(" Before calling port put method"),UVM_LOW)33. trans_out.put(trans); // Step-2: Calling put Method to send trans to comp_b34. `uvm_info(get_type_name(),$sformatf(" After calling port put method"),UVM_LOW) |

Line 32 and 34 are before and after calling the trans_out.put() method. In the log, we can see that line number 32 got executed at 0ns time, whereas line 34 got executed at 100ns. This shows that trans_out.put() got blocked for 100ns. This shows the blocking nature of blocking the port and imp port.

❮ Previous Next ❯