1.Lexical conventions

2.1 Lexical tokens ……………………………………………………………………………………………………………… 6

2.2 White space…………………………………………………………………………………………………………………. 6

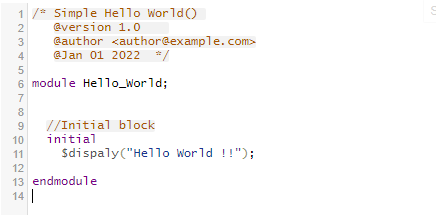

2.3 Comments …………………………………………………………………………………………………………………… 6

2.4 Operators…………………………………………………………………………………………………………………….. 6

2.5 Numbers……………………………………………………………………………………………………………………… 6

2.6 Strings ………………………………………………………………………………………………………………………. 10

System tasks and functions

Done:

3. Data types…………………………………………………………………………………………………………………………. 20

3.1 Value set……………………………………………………………………………………………………………………. 20

3.2 Nets and variables ………………………………………………………………………………………………………. 20

3.3 Vectors ……………………………………………………………………………………………………………………… 23

Variable Data Types in detail ( regs, Integers, reals, times, and realtimes)

3.10 Arrays……………………………………………………………………………………………………………………….. 33

3.11 Parameters…………………………………………………………………………………………………………………. 34

10. Tasks and functions………………………………………………………………………………………………………….. 151

10.1 Distinctions between tasks and functions …………………………………………………………………….. 151

10.2 Tasks and task enabling …………………………………………………………………………………………….. 151

10.3 Functions and function calling……………………………………………………………………………………. 156

12. Hierarchical structures ……………………………………………………………………………………………………… 165

12.1 Modules…………………………………………………………………………………………………………………… 165

12.2 Overriding module parameter values…………………………………………………………………………… 179

12.3 Ports ……………………………………………………………………………………………………………………….. 184

12.4 Hierarchical names …………………………………………………………………………………………………… 192

12.5 Upwards name referencing ………………………………………………………………………………………… 195

12.6 Scope rules ……………………………………………………………………………………………………………… 197

This can be done later

17. System tasks and functions ……………………………………………………………………………………………….. 277

17.1 Display system tasks …………………………………………………………………………………………………. 277

17.2 File input-output system tasks and functions………………………………………………………………… 286

17.3 Timescale system tasks ……………………………………………………………………………………………… 297

17.4 Simulation control system tasks………………………………………………………………………………….. 301

17.5 PLA modeling system tasks……………………………………………………………………………………….. 302

17.6 Stochastic analysis tasks ……………………………………………………………………………………………. 306

17.7 Simulation time system functions……………………………………………………………………………….. 308

17.8 Conversion functions ………………………………………………………………………………………………… 310

17.9 Probabilistic distribution functions ……………………………………………………………………………… 311

17.10 Command line input………………………………………………………………………………………………… 320

6. Assignments……………………………………………………………………………………………………………………… 69

6.1 Continuous assignments………………………………………………………………………………………………. 69

6.2 Procedural assignments……………………………………………………………………………………………….. 73

5. Scheduling semantics…………………………………………………………………………………………………………. 64

5.1 Execution of a model ………………………………………………………………………………………………….. 64

5.2 Event simulation ………………………………………………………………………………………………………… 64

5.3 The stratified event queue……………………………………………………………………………………………. 64

5.4 The Verilog simulation reference model ……………………………………………………………………….. 65

5.5 Race conditions………………………………………………………………………………………………………….. 66

5.6 Scheduling implication of assignments …………………………………………………………………………. 66

Modeling

1.DataFlow modeling

assignments,delays, expressions, operators and operands (LRM chapter – 4)

2. Behavioral modeling

9. Behavioral modeling………………………………………………………………………………………………………… 118

9.1 Behavioral model overview ……………………………………………………………………………………….. 118

9.2 Procedural assignments……………………………………………………………………………………………… 119

9.3 Procedural continuous assignments …………………………………………………………………………….. 124

9.4 Conditional statement ……………………………………………………………………………………………….. 127

9.5 Case statement …………………………………………………………………………………………………………. 130

9.6 Looping statements …………………………………………………………………………………………………… 134

9.7 Procedural timing controls…………………………………………………………………………………………. 136

9.8 Block statements ………………………………………………………………………………………………………. 145

9.9 Structured procedures ……………………………………………………………………………………………….. 148

3. Gate level modeling

7. Gate and switch level modeling…………………………………………………………………………………………… 75

7.1 Gate and switch declaration syntax……………………………………………………………………………….. 75

7.2 and, nand, nor, or, xor, and xnor gates…………………………………………………………………………… 81

7.3 buf and not gates ………………………………………………………………………………………………………… 82

7.4 bufif1, bufif0, notif1, and notif0 gates…………………………………………………………………………… 83

7.5 MOS switches ……………………………………………………………………………………………………………. 84

7.6 Bidirectional pass switches ………………………………………………………………………………………….. 86

7.7 CMOS switches …………………………………………………………………………………………………………. 86

7.8 pullup and pulldown sources ……………………………………………………………………………………….. 87

7.9 Logic strength modeling ……………………………………………………………………………………………… 88

7.10 Strengths and values of combined signals ……………………………………………………………………… 89

7.11 Strength reduction by nonresistive devices…………………………………………………………………… 102

7.12 Strength reduction by resistive devices………………………………………………………………………… 102

7.13 Strengths of net types………………………………………………………………………………………………… 102

7.14 Gate and net delays …………………………………………………………………………………………………… 103

4. switch level modelling

FSM:

8. User-defined primitives (UDPs) ………………………………………………………………………………………… 107

8.1 UDP definition …………………………………………………………………………………………………………. 107

8.2 Combinational UDPs ………………………………………………………………………………………………… 111

8.3 Level-sensitive sequential UDPs ………………………………………………………………………………… 112

8.4 Edge-sensitive sequential UDPs …………………………………………………………………………………. 112

8.5 Sequential UDP initialization …………………………………………………………………………………….. 113

8.6 UDP instances………………………………………………………………………………………………………….. 115

8.7 Mixing level-sensitive and edge-sensitive descriptions………………………………………………….. 116

8.8 Level-sensitive dominance…………………………………………………………………………………………. 117

18. Value change dump (VCD) files………………………………………………………………………………………… 324

18.1 Creating the four state value change dump file …………………………………………………………….. 324

18.2 Format of the four state VCD file ……………………………………………………………………………….. 329

18.3 Creating the extended value change dump file ……………………………………………………………… 339

18.4 Format of the extended VCD file………………………………………………………………………………… 343

19. Compiler directives………………………………………………………………………………………………………….. 350

19.1 `celldefine and `endcelldefine…………………………………………………………………………………….. 350

19.2 `default_nettype ……………………………………………………………………………………………………….. 350

19.3 `define and `undef …………………………………………………………………………………………………….. 351

19.4 `ifdef, `else, `elsif, `endif, `ifndef ……………………………………………………………………………….. 353

19.5 `include …………………………………………………………………………………………………………………… 357

19.6 `resetall……………………………………………………………………………………………………………………. 357

19.7 `line ………………………………………………………………………………………………………………………… 358

19.8 `timescale ………………………………………………………………………………………………………………… 358

19.9 `unconnected_drive and `nounconnected_drive ……………………………………………………………. 360