Integrating RAL to Agent

Table of Contents

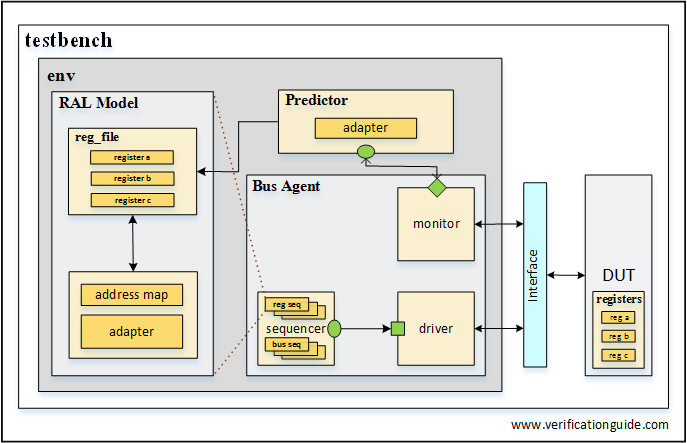

Once after the RAL implementation, RAL has to be connected with the Bus Agent. This section describes connecting RAL with the sequencer and monitor of the bus.

Integrating Bus Sequencers

All integration approaches require a register model to be configured with one or more bus sequencers.

The register model becomes a property of a uvm_reg_sequence subtype that executes

- Directly on a bus sequencer, if there is only one bus interface providing access to the DUT registers

- As a virtual sequence, if there are one or more bus interfaces providing access to the DUT registers;

- As a register sequence running

Integrating the Register Model with a Bus Monitor

By default, the register model updates its mirror copy of the register values implicitly. Every time a register is read or written through the register model, its mirror value is updated.

If other agents on the bus interface perform read and write transactions outside the context of the register model, the register model must learn of these bus operations to update its mirror accordingly.

- Integration is accomplished by first instantiating a uvm_reg_predictor component

- uvm_reg_predictor component is then connected to the bus monitor’s analysis port

class tb_env extends uvm_env;

reg_model regmodel;

uvm_reg_predictor#(ahb_trans) ahb2reg_predictor;

reg2ahb_adapter reg_adapter;

ahb_agent ahb;

virtual function void build_phase(uvm_phase phase);

ahb2reg_predictor = new(“ahb2reg_predictor”, this);

endfunction

virtual function void connect_phase(uvm_phase phase);

if (regmodel.get_parent() == null) begin

reg_adapter = reg2ahb_adapter::type_id::create(“reg_adapter”,,get_full_name());

...

ahb2reg_predictor.map = regmodel.AHB;

ahb2reg_predictor.adapter = reg_adapter;

ahb.monitor.ap.connect(ahb2reg_predictor.bus_in);

end

...

endfunction

...

endclass