Packaging and Integrating a Register Model

Packaging a Register Model

The following practices are recommended, but not required.

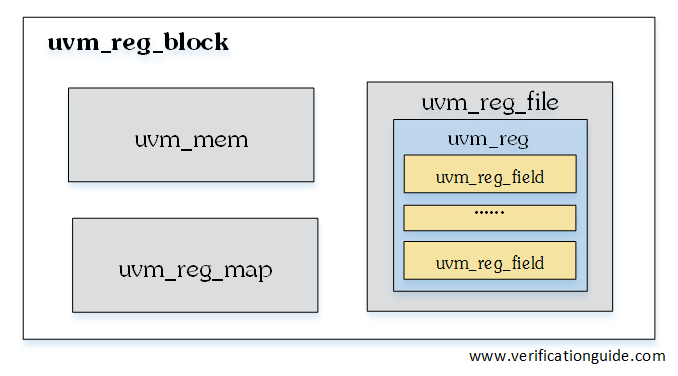

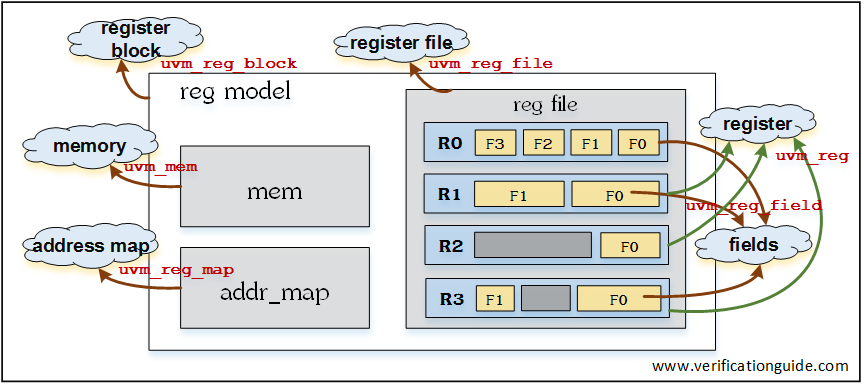

- Block types, and all the register, register file, and memory types they require, should be located in separate packages

- Register, register file, and memory types shared by more than one block type should be located in separate packages

- A header file, with all the required import statements to use the register model, should be generated

- A lengthy build() method may be split into several, shorter sub-methods. The sub-methods shall be declared local and called by the build() method

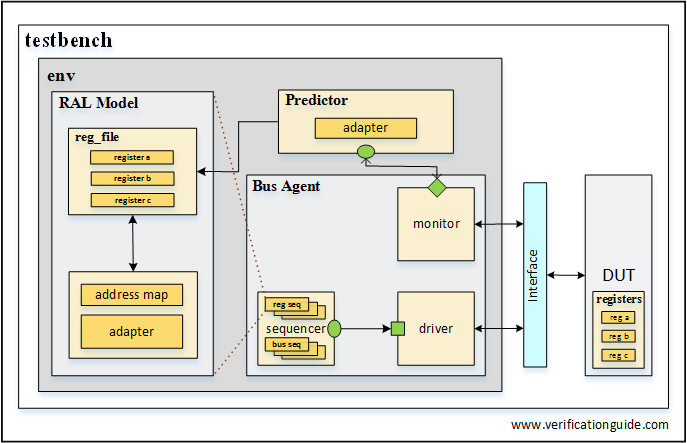

Integrating a Register Model

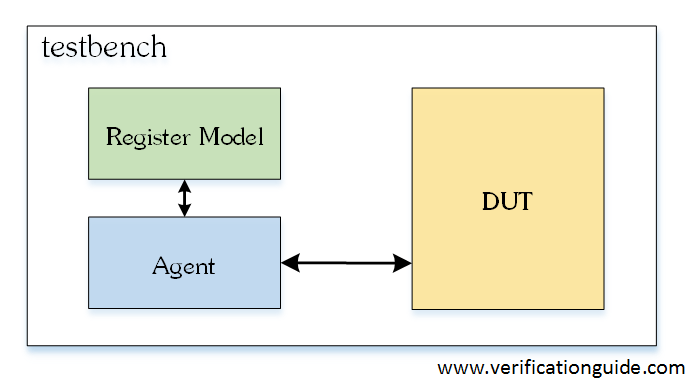

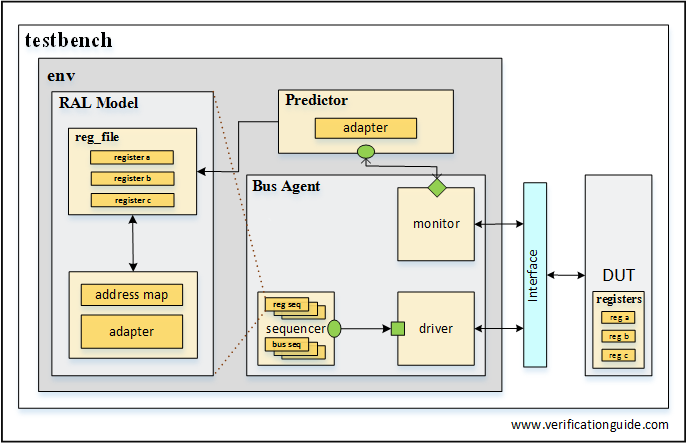

- A register model must be integrated with the bus agent

- The integration with the bus agent must only be done on root blocks

- Root blocks model the entire DUT and they are the only ones who have access to and knowledge of the externally-visible address maps.i.e in the environment of the testbench

class tb_env extends uvm_env;

reg_model regmodel;

subblk_env subblk;

virtual function void build_phase(uvm_phase phase);

if (regmodel == null) begin

regmodel = reg_model::type_id::create(“regmodel”, this);

regmodel.build();

regmodel.lock_model();

end

subblk = subblk_env::type_id::create(“subblk”, this);

subblk.regmodel = regmodel.subblk;

endfunction

endclass